工程师正以各种妙招利用图形处理器的强大功能来满足人工智能的计算需求。

人们正在对计算机芯片进行调整,以便为人工智能应用做更多更快的并行计算

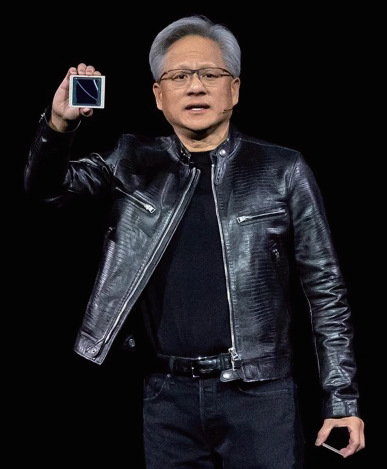

英伟达首席执行官黄仁勋举起该公司新推出的布莱克韦尔图形处理器

2024年3月,12 000多名观众急切地坐进了美国加利福尼亚州圣何塞的一座体育馆。“我希望你们意识到,这不是一场音乐会。”黄仁勋开玩笑道。他是位于附近圣克拉拉的芯片制造公司英伟达(NVIDIA)的首席执行官。

在接下来的半个小时里,黄仁勋向听众介绍了图形处理器(GPU)的最新讯息,GPU是其公司的标志性计算机芯片,也是过去十年里人工智能(AI)进步的关键。黄仁勋举起该公司2022年的产品,霍珀“超级芯片”(Hopper)。“霍珀改变了世界。”他说。他吊人胃口地停顿片刻,随即展示出另一块便利贴大小、闪耀的黑色长方形物体:“而这是布莱克韦尔(Blackwell)。”台下一片欢呼。

早在2022年,霍珀芯片就在机器学习表现基准测试(MLPerf)中大获全胜,从图像分类到语音识别,它在各个类别中都击败了竞争对手。MLPerf由一系列测试组成,有时被称为人工智能界的奥林匹克竞赛。霍珀芯片甫一上市,那些希望为自家人工智能增效的公司就将其认定为了首选芯片。如今,英伟达承诺,布莱克韦尔芯片在处理特定问题时的速度将比上一代产品快数倍。英伟达加速计算部门产品营销总监戴夫 · 萨尔瓦托(Dave Salvator)表示:“我认为布莱克韦尔芯片将通过更强大的性能以及芯片之间更高效的通信,将我们的人工智能性能提升到一个新的水平。”

在人们对人工智能的影响感到喜忧参半的同时,人工智能芯片市场仍在持续增长。目前,英伟达提供了80%以上的人工智能芯片;在2023年,它售出了55万块霍珀芯片。这些功能强大的芯片每块至少售价3万美元(约合22万人民币),主要用于数据中心而非个人电脑。2024年,英伟达的市值飙升至2万多亿美元(约合14万亿人民币),成为全球市值第三高的公司,排在亚马逊和谷歌母公司字母表(Alphabet)等巨头之前。

英伟达的布莱克韦尔芯片是硬件开发浪潮的一部分,而这股浪潮是各家公司努力跟上并支持人工智能革命的结果。在过去的十年中,人工智能的大部分进步与其说是来自巧妙的编码技巧,不如说是来自“越大越好”这一简单的原则。大语言模型越来越多地使用更大的数据集进行训练,也越来越需要更强的计算能力。据估计,美国公司开放人工智能(OpenAI)的最新模型GPT-4所需的算力是其前代模型的100倍。

元平台(Meta)等公司已经建立了以英伟达GPU为基础的数据中心。包括谷歌、IBM,以及众多规模较小的公司在内的一系列其他公司,则都设计出了自家的人工智能芯片;元平台目前也在开发自己的芯片。与此同时,研究人员也在尝试各种芯片设计,其中一些是针对小型设备进行的优化设计。随着人工智能的应用场合不再局限于云计算中心,转而进入移动设备,意大利米兰理工大学的计算机工程师克里斯蒂娜 · 西尔瓦诺(Cristina Silvano)表示:“我认为GPU已经不够用了。”

这些芯片都有一个共同点:它们采用了包括并行计算、更易访问的内存和数字速记等各种技巧,以帮助它们克服传统计算的速度障碍。

芯片的更新换代

过去十年的深度学习革命在很大程度上得益于对传统计算主力——中央处理器(CPU)——的突破。

CPU本质上是一台微小的命令执行机器。加拿大多伦多大学的计算机工程师沃恩? · ?贝茨(Vaughn Betz)解释道:“简单来讲,它会查看一条指令,然后问自己,‘这条指令是要我做什么?’”在最基本的层面上,CPU通过翻转晶体管来执行指令,晶体管是简单的电开关,用开来表示“1”,关来表示“0”。仅通过这种二进制操作,晶体管就可以执行非常复杂的计算。

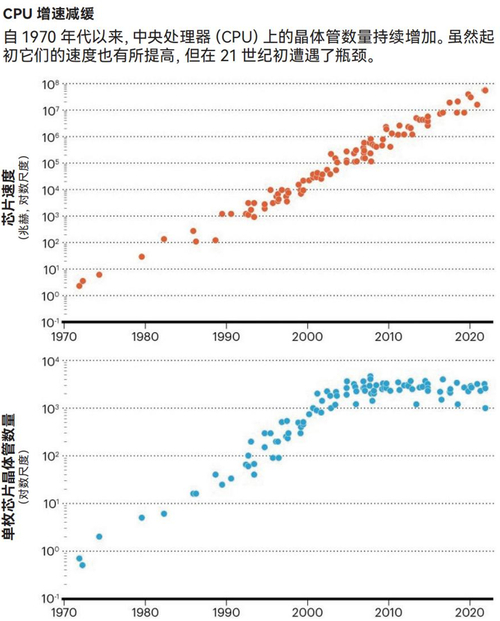

CPU的功率和效率主要取决于晶体管的尺寸——较小的晶体管翻转速度更快,而且可以更密集地封装在芯片上。如今,最先进的晶体管仅有45×20 纳米大小,不比它的原子构件大多少。顶级CPU每平方毫米可封装一亿多个晶体管,每秒可执行约一万亿次浮点运算。

自20世纪70年代以来,CPU的性能呈指数级增长。随着晶体管的缩小,它们在芯片上的密度每两年翻一番(这一趋势被称为摩尔定律),而更小的晶体管速度也变得更快(这是登纳德缩放定律造成的结果)。CPU的进步太过迅猛,以至于定制设计其他类型的芯片变得毫无意义。加州大学洛杉矶分校的计算机工程师丛京生(Jason Cong)表示:“当你设计出一个特殊电路时,CPU的速度已经比之前快了两倍。”但在2005年左右,更小的晶体管不再变得更快,而在过去几年中,工程师开始担忧无法将晶体管做得更小,因为这些设备渐渐触及基本物理定律的极限。

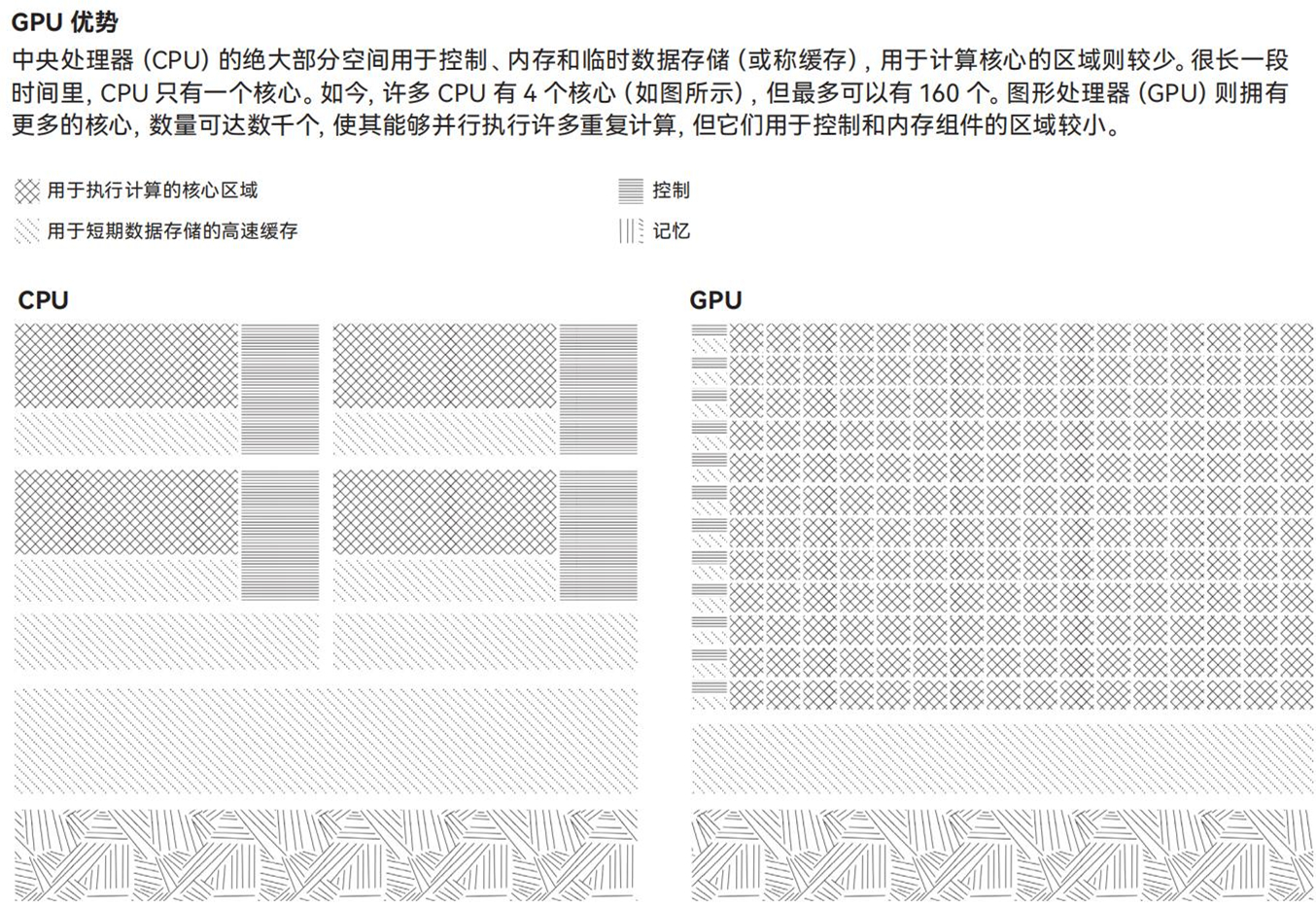

CPU进展的放缓促使计算机工程师开始认真考虑其他类型的芯片。GPU的早期版本早在20世纪70年代末就已出现,其设计目的是为视频游戏执行重复计算,例如尽快渲染屏幕上像素的颜色。与CPU按顺序处理指令不同,GPU能够并行处理更多的指令。

一般来说,CPU有几个功能强大的“核心”来执行计算。每个独立的处理单元接收指令,并由多个缓存提供支持,这些缓存可在短期内存储数据。这种架构使得CPU非常适合复杂的计算。相比之下,GPU拥有数百或数千个较小的核心,每个核心配备的缓存等提供支持的辅助系统较少。大量的较小核心使得GPU能够并行执行许多简单、重复的计算,速度远快于CPU。(GPU所使用的这种不同计算方式需要不同的计算机代码。萨尔瓦托指出,英伟达从事代码编写的软件工程师数量是其硬件工程师数量的两倍。)

多伦多大学的计算机科学家杰弗里 · 辛顿(Geoffrey Hinton)是神经网络(受大脑启发的算法)的早期倡导者之一。2012年,他向自己当时的学生亚历克斯 · 克里泽夫斯基(Alex Krizhevsky)发起挑战,希望对方赢得一年一度的图网竞赛(ImageNet),该赛的目标是训练计算机正确识别日常物体的图像。当时,使用CPU的程序最多只能达到75%的准确率。克里泽夫斯基意识到,使用GPU训练的神经网络人工智能可能会做得更好,因为机器学习的基础是简单的重复计算。

克里泽夫斯基和他的合作者使用了两块GPU来训练他们的神经网络,即亚历克斯网(AlexNet)。他们的人工智能拥有6000万个参数(即人工智能模型用来进行预测的内部变量),这在当时是史无前例的。AlexNet在比赛中脱颖而出,准确率高达85%,它能够可靠地区分相似的图像(如豹和美洲豹),这一能力令世人惊叹。一两年后,图网竞赛的所有参赛者都开始使用GPU;自那时起,人工智能的研究者就开始大量地使用这些芯片。

尽管GPU和CPU一样,仍然受到晶体管的限制,但它们的并行计算能力使它们能够加快人工智能执行任务的速度。为了训练拥有1750亿个参数的大语言模型GPT-3,OpenAI的研究人员不得不连续一个月运行1024块GPU,耗资数百万美元。这些GPU总共执行了1023次浮点运算。而在同类CPU上,同样的训练需要花费数百到数千倍的时间。贝茨说:“有了更大的算力,你就可以训练更大的网络,这样它们就会越来越好。”例如,2023年3月发布的GPT-4的参数量达到了惊人的1.8万亿个,比上一代模型增加了10倍。

虽然GPU在人工智能革命中起到了关键作用,但它们并不是唯一的主角。随着人工智能应用的普及,人工智能芯片也在不断涌现。

芯片的百花齐放

有时,给芯片输入指令的时间并不充裕。现场可编程逻辑门阵列(FPGA)的发明使得计算机工程师可以对芯片电路进行编程,让其遵循特定指令,而无需外部指令。贝茨表示:“像CPU或GPU这样的芯片必须等待外部指令,而FPGA可以直接执行。”

对丛京生来说,FPGA“就像一盒乐高积木”。无论是洗衣机传感器,还是用于引导自动驾驶汽车的人工智能,工程师都可以将FPGA电路逐一构建成他们所能想象的任何设计。然而,与GPU等电路不可调整的人工智能芯片相比,FPGA的速度较慢,效率也较低。包括阿尔特拉(Altera,英特尔在圣何塞的子公司)在内的公司都将FPGA用于包括医学成像在内的各种人工智能应用;研究人员发现它们在处理粒子对撞机数据等小众任务时非常有用。西尔瓦诺说,FPGA的易编程性也使其非常适用于原型设计。她经常在开始着手烦琐的芯片制造过程之前,先用FPGA设计人工智能芯片。

西尔瓦诺还致力于开发体积更小的人工智能芯片,提高它们的计算效率,从而改进移动设备。她说,要是能在手机上加装一块完整的GPU自然最好,但能源成本和价格让这件事变得不可行。精简的人工智能芯片可以通过处理人工智能应用的繁琐任务(如图像识别)来辅助手机的CPU,而无须向云端发送数据。

人工智能芯片处理的最费力的工作可能是乘法运算。2010年,谷歌遇到了一个问题:公司希望为大量的日常用户进行语音转录。如果要训练人工智能自动处理这项工作,除却其他艰巨的任务外,还需要对大量数字进行乘法运算。“如果只使用CPU,我们的服务器数量就必须翻倍,”谷歌的计算机工程师诺曼 · 尤派(Norm Jouppi)说,“这听起来不是什么好主意。”于是,尤派领导开发了一种名为张量处理器(TPU)的新型芯片,作为谷歌人工智能的运行平台。

TPU专为支撑人工智能的算术运算而设计。当TPU接收到一条指令时,它可以执行超过十万次运算,而非仅执行一次运算。(TPU的数学多任务处理能力是专门设计的电路和软件的结果;如今,许多为人工智能应用设计的GPU——如布莱克韦尔芯片——也具备类似的能力。)TPU仅需有限指令就能执行大量运算的能力令谷歌得以为其许多人工智能项目增速,而不仅仅限于语音转录服务。

为了进一步加速计算,许多人工智能芯片(如TPU和GPU)都使用了一种数字速记法。CPU通常以64位格式记录数字,即64个0或1的槽位,每一个槽位都需要表示任何给定的数字。使用位数更少的数据格式可能会降低计算的精度,因此通用芯片都使用64位格式。

但是,贝茨指出,如果你能减少精度,“那么硬件就会变得更简单、更小巧、功耗更低”。例如,列出DNA序列原则上只需要2位格式,因为遗传信息只有四种可能性:碱基A、T、G或C(分别表示为00、01、10或11)。丛京生设计的一种使用2位格式比对基因组数据的FPGA芯片,比使用64位格式的同类CPU速度快了28倍。为了加速机器学习的计算速度,工程师降低了芯片的精度,TPU依赖于专门的16位格式。对于诸如布莱克韦尔这样的最新一代芯片,用户甚至可以从4位到64位的一系列格式中选择最适合所需计算精度的格式。

芯片的前景广大

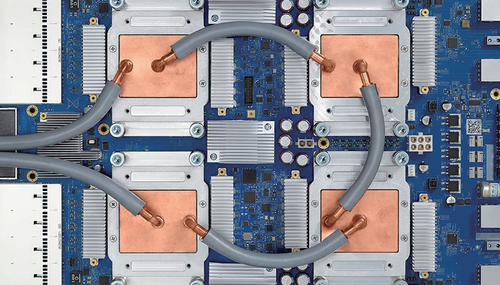

人工智能芯片的另一个设计特点是:避免记忆过多。在执行计算的微处理器和存储数据的存储器之间来回传输数据非常耗时耗能。为了解决这个问题,许多GPU在单个芯片上直接连接了大量内存——英伟达的布莱克韦尔芯片拥有大约200GB的内存。当人工智能芯片安装在服务器中时,它们还可以共享内存,使单个芯片之间的联网变得更加容易,也减少电力消耗。谷歌将近9000个TPU连接在了一个“集群”(pod)中。

这么多电子在电路中移动是个巨大的负担,其耗电量不是个小问题。准确的数据很难确定,但据估计,GPT-3的训练消耗了1300兆瓦时(MWh)的电力。(英国一个普通家庭的年耗电量约为3兆瓦时。)即使在训练之后,使用人工智能应用程序仍然会消耗大量能源。尽管芯片设计的进步可以提高效率,但随着模型规模的不断扩大,人工智能的能源成本仍在逐年增加。

GPU等人工智能芯片的兴起并不意味着CPU的终结。相反,即使是最基本的芯片类型之间的界限也在变得越来越模糊——现代CPU在并行计算方面比早期版本更胜一筹,而GPU也变得比过去更加多才多艺。“大家都在互相借鉴对方的技术。”贝茨表示。英伟达的布莱克韦尔芯片的某个版本直接将GPU与CPU配对使用,世界上最强大的超级计算机——位于美国田纳西州橡树岭国家实验室的“前沿”(Frontier)——则依赖于CPU和GPU的混合使用。

鉴于过去十年的变化速度,研究人员表示很难预测芯片的未来:未来可能会出现使用光而非电子的光学芯片或是量子计算芯片。与此同时,一些人表示,让公众更多地了解人工智能硬件有助于揭开这个领域的神秘面纱,并纠正大众对人工智能无所不能的误解。西尔瓦诺说:“你可以更好地向人们传达,人工智能并不是什么魔法。”

尤派说,从根本上讲,人工智能只是一堆电线和电子,不太可能占领世界。“你可以直接拔掉电源。”他说。他希望硬件能够不断改进,这反过来将有助于加速人工智能在科学领域的应用。“我对此充满热情,”尤派说,“我对未来的发展充满期待。”

资料来源Nature